|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 [ 50 ] 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

\l-biumom IZ-ой mom

одном элементе - 3. Вторые ступени laquo;и raquo; показаны в виде общих линий, соединяющих выходы элементов, причем, как видно из рисунка, максимальное количество объединенных между собой выходов в этом построении сумматора - четыре.

Одноразрядный сумматор, изображенный на рис. 2-13, получает только прямые сигналы входных переменных fc, с, е и вырабатывает инверсные сигналы ВиЕ. При необходимости их можно было бы инвертировать с помощью двух дополнительных элементов laquo;и-не raquo;; но, как будет видно из раздела 2.2.3, в этом может и не быть нужды. Без этих дополнительных инверторов схема рис. 2-13 содержит 7 элементов laquo;и-не raquo;. Возможно, однако, что существуют и более экономные построения.

Если вместо элементов laquo;и raquo;, laquo;или raquo; ji laquo;нет raquo; применяется какая-нибудь другая система элементов, то построение

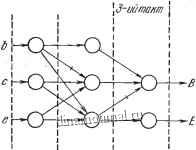

сумматора будет, разумеется, совсем не таким, как рассматривалось выше. Не имея возможности останавливаться на разнообразных логических схемах, которые приходится строить в этих случаях, приведем лишь один интересный пример. На рис. 2-14 показано построение одноразрядного двоичного сумматора из парамет-ронов. Каждый параметров представлен здесь кружком с нечетным количеством входов (один или три) и одним выходом. Напомним, что выходной сигнал параметрона совпадает по фазе с большинством сигналов на входах; таким образом, если параметрон имеет три входа, то при наличии единиц на двух или трех из них на выходе появляется единица, а при наличии на входах двух или трех нулей выходной сигнал есть нуль. Черточка на линии, соединяющей выход одного параметрона со входом другого, означает на

Рис. 2-14. Построение двоичного одноразрядного сумматора из параметронов.

рисунке, что обмотки здесь соединены накрест, т. е. что на вход второго параметрона подается инверсия от выходного сигнала первого.

В том, что схема рис. 2-14 действительно является одноразрядным двоичным сумматором, легко убедиться перебором всех комбинаций входных переменных в соответствии с таблицей 2-1 (стр. 147).

В схеме рис. 2-14 имеется ряд laquo;лишних raquo; ступеней - параметроны с одиночными входами, не выполняющие никаких логических функций. Стоят они потому, что схема сумматора работает в три такта (как и большинство схем на параметронах), и по всем цепям должны быть обеспечены равные запаздывания.

Входные сигналы в схему сумматора подаются здесь все одновременно, выходные же сигналы (В, Е) появляются оба одновременно, но с опозданием на 3 такта относительно входных. Однако это запаздывание не носит принципиального характера, а связано только с техническими особенностями работы параметронов. Если бы вместо параметронов применялись элементы потенциального типа, выполняющие те же логические функции, что и параметроны, то никакого запаздывания сигналов в построении рис. 2-14 не было бы, кроме естественных задержек на срабатывание элементов. Аналогичное положение возникает при построении комбинационных сумматоров из феррито-диодных или феррито-транзисторных элементов. .

Вообще говоря, имея любую функционально полную систему элементов, всегда можно построить из этих элементов схемы, выполняющие логические операции laquo;и raquo;, laquo;или raquo; и laquo;нет raquo;. Затем из таких схем можно составить сумматор в соответствии с одним из построений рис. 2-4 - 2-12. Читателю предлагается испытать этот путь для случая использования параметронов. Сопоставление полученных результатов с построением рис. 2-14 покажет, что такой путь является далеко не наилучшим и что каждый раз, когда применяется новая система логических элементов, приходится заново искать подходящие построения сумматоров.

2.2.3. Некоторые общие свойства двоичных одноразрядных сумматоров комбинационного типа. Рассматривая таблицу 2-1 на стр. 147, нетрудно убедиться, что обе

переключательные функции, формируемые двоичным одноразрядным сумматором, являются функциями самодвойственными. Это означает, что инвертирование всех входных переменных-цифр слагаемых Ьи с и цифры переноса в данный разряд е - приводит к тому, что на выходах схемы вместо цифры суммы В и цифры переноса в следуюший-разряд Е будут формироваться их инверсии.

Например, при Ь = с = е О на выходах схемы нормально получаем В = О и = О (первая строка таблицы 2-1); инвертирование входных переменных, т. е. подача на входы вместо сигналов Ь, с, е их инверсий b = с = ё - 1, приведет к тому, что на обоих выходах получатся сигналы laquo;1 raquo; (последняя строка таблицы), т. е. фактически ВиЕ. Если b = с = О, а е = 1, то на выходах нормально получаем В = 1, = О (вторая строка таблицы); при подаче на входы Ь, с, е инверсий от входных величин, т. е. сигналов b = с = 1,ё = 0, на выходе В получим laquo;О raquo;, на выходе JE - laquo;1 raquo;(см. предпоследнюю строку таблицы), т. е. инверсии выходных сигналов Б и Е, и т. R.

Это свойство двоичных одноразрядных сумматоров .иногда используется следующим образом.

Представим себе, что параллельный сумматор строится из одноразрядных сумматоров такого типа, как показано на рис. 2-7, а или б или на рис. 2-8, причем элементы laquo;и raquo; и laquo;или raquo; выполняются из диодов, а инвертором служит ламповый или транзисторный усилитель постоянного тока; предположим, кроме того, что триггерные регистры, от которых получаются цифры слагаемых, выполнены из симметричных статических триггеров, так что в любом раз-р.яде инверсии входных переменных b и с легко доступны.

На рисунках, иллюстрирующих построение одноразрядных сумматоров, показано, что выходной сигнал переноса Е получается на выходе одного из диодных логических элементов, а входной сигнал переноса е поступает на входы других диодных логических элементов. Однако в действительности в рассматриваемом случае нельзя непосредственно соединить входы переноса каждого из разрядов с выходом переноса соседнего младшего разряда, как это по логике должно быть сделано в параллельном сумматоре: слишком много каскадов диодных логических

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 [ 50 ] 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |