|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 [ 169 ] 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

образуют схему формирования ответа. Если пробег сигна-ловзайма оборвется в одном из трех младших разрядов, то эта схема сформирует импульс-ответ, обозначающий, что специального времени для преобразования частного можно не отводить (мы полагаем, что распространение сигналов займа через 2 разряда происходит достаточно быстро и по времени укладывается в такт сдвига). Вероятность же того, что все три младшие разряда до преобразования содержали нули, равна всего Vs- Таким образом, общая вероятность того, что в схеме рис. 5-4 в некотором шаге деления потребуется специальное время для выполнения преобразования

частного, меньше чем g g - меньше /le. Скажем, при выполнении операций с 30 двоичными разрядами, такие случаи встречаются в среднем в одном-двух (из тридцати) циклах деления.

О некоторых дальнейших возможностях развития этого метода ускорения деления говорится в 5.1.8.

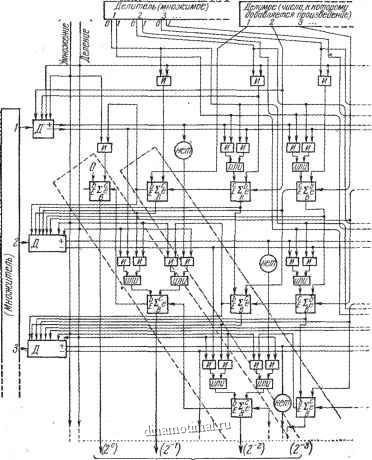

5,1.5. Аппаратный метод 2-го порядка для ускорения двоичного деления. Если для ускорения умножения применяется метод второго порядка, то оборудование множительного устройства желательно использовать и для ускорения деления. При этом весьма полезной оказывается идея использования избыточных цифр частного. Одно из возможных решений иллюстрируется рис. 5-5 *). Устройство, показанное на этом рисунке, представляет собой несколько усложненную схему множительного устройства рис. 4-11 (стр. 448), описанного в разделе 4.5.2. На рис. 5-5 показан только левый верхний угол ромба.

Принцип выполнения деления в приведенной схеме состоит в следующем.

На входах каждого горизонтального ряда одноразрядных сумматоров имеются логические элементы laquo;и - или raquo;, которые позволяют передать на входы сумматоров либо прямой, либо обратный код делителя; при этом данный ряд сумматоров будет выполнять либо добавление, либо вычитание делителя, сдвинутого соответствующим образом.

*) К а р ц е в М. А., Авт. св. СССР, кл. 42т, 14, с приоритетом от 4.09.1959 г., № 129390.

От схемы управленш

Результат

Рис. 5-5. Устройство для выполнения умножения и деления с исполь-. зованием методов ускорения 2-го порядка.

Работой логических элементов управляют дешифраторы сигналов управления ( laquo;Д raquo;), имеющиеся в каждом ряду. На входы дешифраторов сигналы подаются с выходов старших разрядов предьщущего ряда сумматоров. В зависимости от комбинации цифр на входах, т. е. в зависимости от старших разрядов предьщущего остатка, в дешифраторе формируется очередная цифра частного: -f- 1, -1 или 0. Если цифра частного -Ь 1, то дешифратор вырабатывает сигнал laquo;- raquo;, и в следующем ряду сумматоров сдвинутый делитель вычитается из предьщущего остатка; если цифра частного есть-1, то дешифратор вырабатывает сигнал laquo;-- raquo;, и в следующем ряду сумматоров сдвинутый делитель добавляется к предьщущему остатку; если цифра частного есть О, то дешифратор не вырабатывает никаких сигналов, и следующий ряд сумматоров не производит ни сложения, ни вычитания. В зависимости от цифр, которые получатся на выходе следующего ряда сумматоров, та или иная цифра частного сформируется в следующем дешифраторе сигналов управления и т. д.

Существенным здесь является то, что сигналы переноса распространяются не вдоль горизонтальных рядов одноразрядных сумматоров (как было, например, в множительном устройстве рис. 4-10 на стр. 445), а по вертикали (так же, как на рис. 4-11). Благодаря этому все сумматоры некоторого горизонтального ряда срабатьшают одновременно. Сразу вслед за этим начинается срабатывание дешифратора сигналов управления следующего ряда. Если бы переносы распространялись по горизонтали, то после подачи сигнала laquo;-[- raquo; или laquo;- raquo; на данный ряд сумматоров нужно было бы выждать, пока сигналы переноса пройдут вдоль этого ряда от младших разрядов к старшим, и только затем мог бы начать работу следующий дешифратор сигналов управления; деление при этом выполнялось бы слишком медленно.

Однако в рассматриваемой схеме каждый очередной остаток получается в виде двух чисел: числа, составленного из цифр на выходах В предьщущего ряда сумматоров, и числа, составленного из цифр на выходах Е. Для определения очередной цифры частного приходится пользоваться теми же приемами, которые рассматривались в 5.1.3 и 5.1.4. Во всех рядах, кроме первого, в дешифратор сигналов

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 [ 169 ] 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |