|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 [ 147 ] 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

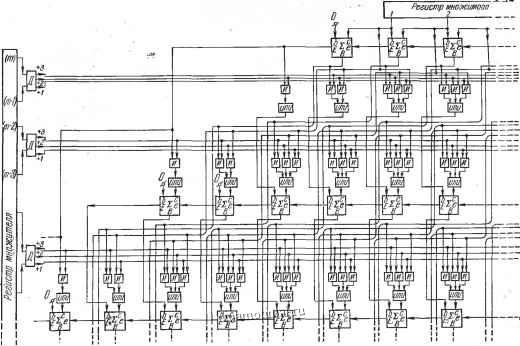

данного ряда, цифра на выходе Е второго слева однораз-оядного сумматора этого же ряда и цифра на выходе крайнего левого сумматора следующего ряда. Ряд сумматоров, обведенный пунктирной рамкой, свертывает тройку чисел, составленных из этих цифр, в пару чисел.

После этого для каждого разряда произведения остаются уже по 2 цифры; в старшей части - это цифры на выходах В и Е двух соседних одноразрядных сумматоров дополнительного ряда, в младшей части - это цифры на выходах В к Е двух соседних одноразрядных сумматоров младшего (самого нижнего) из основных рядов. Два числа,составленные из указанных цифр, суммируются специальным параллельным сумматором, который на рис. 4-И тоже обведен пунктиром и размещен левее и ниже первого из дополнительных рядов. На его выходах получается окончательное произведение.

Главное достоинство рассматриваемого построения по сравнению с описанными ранее состоит в том, что в нем легко достигнуть одновременности срабатывания всех одноразрядных сумматоров любого из основных рядов. В той схеме, которая приведена на рис. 4-11, этого непосредственно не получается: в первом (верхнем) ряду все одноразрядные сумматоры срабатывают одновременно, но в тот же момент времени срабатывают и крайние правые сумматоры всех остальных рядов; дальше laquo;волна raquo; установления напряжений распространяется сверху вниз и справа налево. Однако, введя элементы задержки перед входами крайних правых сумматоров, легко уравнять времена для одноразрядных сумматоров в каждом из горизонтальных рядов. Если же получения 2т-разрядного произведения не требуется и из схемы можно исключить правую часть ромба (как это было описано применительно к рис. 4-9), то одновременность срабатывания одноразрядных сумматоров в каждом из горизонтальных рядов получается сама собой.

Эта особенность построения, приведенного на рис. 4-11, важна с двух точек зрения. Во-первых, ею можно воспользоваться для того, чтобы применить в схеме синхронные апементы импульсного типа. Для каждого ряда сумматоров при этом пришлось бы подбирать свою фазу сигналов синхронизации. Конечно, это связано с определенными затруднениями; но в схемах рис. 4-9 и 4-10 применить синхронные

элементы еще труднее. Во-вторых,- и это главное -ука занное свойство схемы рис. 4-11 позволяет использовать имеющееся в ней оборудование не только для ускорения умножения, но и для ускорения деления (см. раздел 5.2). Ясно, что при тех больших затратах, которые необходимы для осуществления методов 2-го порядка ускорения умножения, очень желательно возможно полнее и эффективнее загрузить все устанавливаемое оборудование. Построения рис. 4-9 и 4-10 такой возможности не дают.

Приведенными схемами не исчерпывается многообразие различных построений, использующих методы ускорения умножения 2-го порядка. Во многих случаях они отличаются одно от другого некоторыми техническими деталями, иногда быстродействием, возможностью или невозможностью применения дополнительного ускорения и т. д., но являются в общем модификациями основного построения, описанного в 4.5.1. Не имея возможности рассмотреть все известные варианты, мы остановимся в 4.5.3 и 4.5.4 на тех из них, которые содержат некоторые новые идеи.

4.5.3. Сокращение количества оборудования и повышение быстродействия путем усложнения логики. В настоящем разделе мы встретимся со сравнительно редким в технике случаем, когда повышение быстродействия сопряжено не с увеличением, а с уменьшением количества необходимого оборудования.

Идея предлагаемого метода иллюстрируется рис. 4-12. Схема, которая приведена здесь, построена по аналогии с рис. 4-9, причем на рисунке изображен только левый верхний угол ромба; остальную часть схемы читатель без труда может достроить самостоятельно.

Верхний рядодноразрядных сумматоров является вспомогательным. В нем выполняется суммирование множимого с удвоенным множимым (сдвинутым на 1 разряд влево) и получается, таким образом, утроенное множимое. Множимое, удвоенное множимое и утроенное множимое поступают на входы первого ряда логических элементов, затем - со сдвигом на 2 разряда влево - на входы второго ряда логических элементов и т. д.

Каждый ряд логических элементов управляется выходными сигналами дешифратора Д. На входы младшего

Рис. 4-12. Вариант множительного;; устройства с использованием метода ускорения умножения 2-го порядка (схема с усложненной логикой).

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 [ 147 ] 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |