|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Однокристальные микроконтроллеры

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 [ 37 ] 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

- Номер A/D канала

00 - канал О

01 - канал 1 10- канал 2 11 - канал 3

- Автоинкремент (активный - 1 )

Программирование аналогового входа

00 -

AINO - канал О

AIN1 - канал 1

AiN2 - канал 2

AIN3 - канал 3

AINO

AIN1

AIN2

AIN3

10

aino-AIN1 -AIN2-

a:N3 -

AINO-AIN1 -AIN2-AIN3-

канал О

канал 2

- канал О

- канал 1

канал 2

канал О

канал 1

- Активация аналогового выхода

(активный - 1 )

Рис. 3.66. Байт контроля и управления

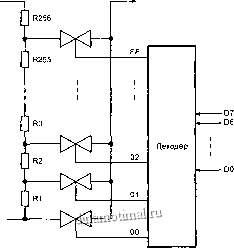

ответвления, которые с помощью переключателей связываются с выходной линией. Управляет схемой декодер ответвлений. Выходное напряжение (DAC out) подается затем на усилитель с автомати-

ческой балансировкой нуля (auto-zeroed unity gain amplifier). Этот усилитель может быть либо включен (через байт контроля и управления), либо переведен в высокоимпедансное (2) состояние выхода.

AGND

DAC OUT

Рис. 3.67. A/D И D/A преобразователь

РЗР2

Байт данных

АОиТ,. VDD--

VREF

AGND

-1-1-1-1-\-----------h

00 01 02 03 04 FE FF

HEX код

Рис. 3.68. D/A преобразоваине

Важно отметить, что D/A преобразователь используется также в процедуре A/D преобразования по методу последовательного приближения. Данный метод подробно описан в литературе, и возвращаться к нему в рамках этой книги нет смысла.

Процедура D/A преобразования показана на рис. 3.68. Любая точка на графике в диапазоне 00h...FFh может быть определена по формуле

АОиТ X\GNGD +

V - V *КГТ *AGND

где Vaout - выходное напряжение D/A преобразователя; Vrep - опорное напряжение; Vagnd - потенциал аналоговой laquo;земли raquo;; D, - соответствующий разряд байта данных.

Обратите внимание также на рис. 3.69. Возможна работа с микросхемой посредством передачи цепочки байтов данных, следующих один за другим. Уровень напряжения, соответствующий заданному, появляется на выходе в момент выдачи сигнала АСК. В момент выдачи сигнала АСК, подтверждающего прием байта контроля и управления (рис. 3.66, control byte) на выходе микросхемы, появляются данные, содержащиеся в регистре DAC с момента окончания предыдущего цикла работы микросхемы.

Slave | А Control | А 1 DATA 1 | DATA 2 | |||||

АОиТ

Высокоимпедансное состояние выхода

Данные из регистра DAC

Данные байта DATA1

Рис. 3.69. Протокол работы в режиме D/A преобразования

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 [ 37 ] 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 |