|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Однокристальные микроконтроллеры

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 [ 34 ] 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

Таблица 3.35. Назначение выводов PCF8574

Символ | Вывод | Описание |

Адресный вход 0 | ||

Адресный вход 1 | ||

Адресный вход 2 | ||

Квази-двунаправленный I/O порт 0 | ||

Квази-двунаправленный I/O порт 1 | ||

Квази-двунаправленный I/O порт 2 | ||

Квази-двунаправленный I/O порт 3 | ||

Общий провод микросхемы | ||

Квази-двунаправленный 1/0 порт 4 | ||

Квази-двунаправленный I/O порт 5 | ||

Квази-двунаправленный I/O порт 6 | ||

Квази-двунаправленный I/O порт 7 | ||

Вывод сигнала прерывания (LOW) | ||

Линия SCL шины PC | ||

Линия SDA шины RC | ||

Питание laquo;+ |

В чем состоит laquo;изюмиика raquo; данной микросхемы? Как известно, прием и передача данных посредством стробирования не вызывает сложностей. Достаточно помещать данные в сдвиговый регистр, а потом осуществлять их движение подачей стробирующих импульсов. Все это так, но главная сложность работы с шиной 1С заключается в том, что затруднительно фиксировать условие Start, свидетельствующее об активизации шины. Если вы помните, в протоколе шины был оставлен служебный адрес 0000 0001, называемый laquo;программный Start raquo;. Работать в условиях программного отслеживания Start-условия достаточно трудно и далеко не всегда оправданно, поэтому в состав микросхемы PCF8574 была введена laquo;изюминка raquo; в виде вывода генерации прерывания (interrupt, INT). Сигнал прерывания сообщит микроконтроллеру о начале активации шины. Таким образом, сторона микросхемы P(F8574, относящаяся к интерфейсу ГС, представляет собой обычное slave-ycтройство (рис. 3.56).

АО А1 А2

SDA

Vdd Vss

Прерывание

LP фильтр

Входной фильтр

Контроллер IC

Сброс по питанию

Регистр-защелка

I/O порт

импульс WRITE

импульс READ

* РО -* Р1 -* Р2 - РЗ - raquo; Р4 - Р5 ~* Р6 -* Р7

Рис. 3.56. Внутреннее устройство микросхемы PCF8574

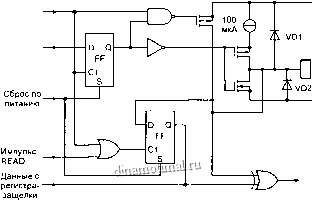

Управляющая схема интерфейса параллельного ввода-вывода показана на рис. 3.57. Обратите внимание: интерфейсные выводы защищены от перегрузки диодами VD1 и VD2.

Импульс WRHE

Данные с регистра-защелки

Р0...Р7

Прерывание

Рис. 3.57. Упрощенная схема параллельного интерфейса микросхемы P(:F8.574

Поговорим теперь о программных способах работы с данной микросхемой. Традиционно начнем с определения slave-адреса (рис. 3.58).

т-1-1-г-1-1-г

S О 1 О 0А2А1А0 0 А

PCF8574

so 1 1 1 А2 А1 АО о А J-1-1-1-1-1-L

PCF8574A Рис. 3.58. Slave-адреса микросхем

Вам могут встретиться две разновидности микросхемы PCF8574 - с буквой laquo;А raquo; и без буквы. Отличаются они только четырьмя старшими битами slave-адреса. Таким образом, если на одной шине будет присутствовать 8 микросхем PCF8574 и 8 микросхем PCF8574A, конфликта это не вызовет. Биты А2...А0 задаются с помощью внешних выводов микросхем.

Запись в порт осуществляется но схеме, представленной на рис. 3.59. laquo;Запись raquo; в данном случае означает, что данные с шины IC появятся на параллельном порте Р0...Р7.

Обратите внимание: данные появляются на выходе порта спустя время после возникновения сигнала АСК (а также заниси в порт). Микроконтроллер должен успеть считать предыдущие данные на ли-пнях Р0...Р7 до появления следующего байта данных.

SCL ЛUUзUU\JAIЛJAГdЛJЛГln

Slave-адрес

SDA S о

Условие START

Запись в порт

Данные выходят с порта

Данные в порт

АСК от slave

Данные в порт

АСК от slave

iACK от jsiave

~)( DATA1 )(~DATA2

Рис. 3.59. Запись данных в порт

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 [ 34 ] 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 |