|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Однокристальные микроконтроллеры

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 [ 23 ] 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

TSA6060

Этот PLL синтезатор мало чем отличается от ранее описанной микросхемы TSA6057, поэтому здесь следует обратить внимание только на интересные отличия.

Для задания частоты генератора может использоваться кварцевый резонатор на 4 или 8 МГц (конфигурируется программно). Частотный диапазон: 500 кГц...30 МГц - для AM и 30...200 МГц - для диапазона FM. Эта микросхема также может использоваться в селекторах метровых волн телевизионных приемников (VHF). Сетка частот может быть указана с шагом 1,10, 25, 50 кГц. Расположение выводов микросхемы TSA6060 показано на рис. 3.28, а назначение выводов - в табл. З.И.

1NLCK [Т | T VCC2 | |

XTAL[2 | T] AMo | |

Vcci и | Tj LOOPi | |

Vee[4 | Tj FMo | |

Fmi [Т | Tj AS | |

DEC [F | T] SCL | |

Дм, [7 | 7] SDA | |

Tj fref |

Piic. 3.28. Расположение выводов микросхемы TSA6060 Таблица 3.11. Назначение выводов микросхемы TSA6060

Символ | Вывод | Описание |

INLCK | in-lock выходной детешр | |

XTAL2 | Вход задающего генератора | |

Vcc, | Вывод питания laquo;+ raquo; | |

Общий провод ( laquo;земля raquo;) | ||

Вход гетеродинного сигнала FM | ||

Вывод развязки предварительного делителя | ||

ш | Вход гетеродинного сигнала ДМ | |

Вывод переключения диапазонов (открытый коллектор) |

Окончание таблицы 3.4

Символ | Вывод | Описание |

f,e, | Выход частоты 40 кГц | |

Линия SDA 2С шины | ||

Линия SCL 2С шины | ||

Селектор slave-адреса на шине IC | ||

Выход FM внешнего петлевого фильтра | ||

LOOP, | Выход усилителя настройки | |

Выход AM внешнего петлевого фильтра | ||

Vcc2 | Вывод питания lt; + raquo; |

В комбинацию битов REF1 и REF2 добавлена сетка частот 50 кГц - комбинация И. Байты информации DATA2 и DAT3 имеют следующую структуру, показанную на рис. 3.29.

В документации приведена табл. 3.12, где указаны тестовые сигналы.

REF1 | REF2 | ТО/AM ОРАМР | в/ЗПГц | ||||

DATA 2 | |||||||

DATA3

Рис. 3.29. Структура информационных байтов

Таблица 3.12. Тестовые сигналы

Функция | |||

Нормальная работа | |||

CP source | |||

CP sink | |||

CP 3-state | |||

CP sink+source | |||

BS = main divider output | |||

BS = reference divider output |

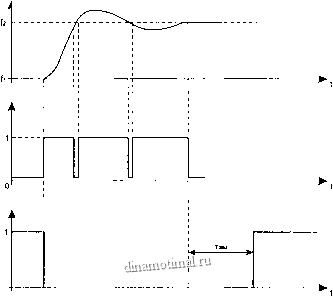

Сигнал INLCK (вывод 1) свидетельствует о захвате фазовым детектором частоты и об удержании ее. Дело в том, что при перестройке с одной частоты на другую требуется некоторое время для того, чтобы фазовый детектор вошел в синхронизацию и поддерживал неизменной частоту гетеродина. Процесс перестройки с частоты f, на частоту показан на рис. 3.30.

График рис. 3.30, а отражает процесс изменения напряжения настройки (по сути это напряжение смещения на варикапах). Уровень напряжения, соответствующий частоте f показан сплошной линией, соответствующий частоте fj - пунктирной линией. Перестройка с частоты на частоту занимает некоторое время, и в момент ее начала сигнал захвата INLCK устанавливается в нулевое состояние. Так как петля ФАПЧ обладает некоторой инерционностью, напряжение laquo;проскакивает raquo; уровень f но через некоторое время снова склоняется к уровню fj. Процесс носит характер колебательного, но постепенно (асимптотически) сходящегося. В моменты пересечения линии f, внутренняя схема lock flag (рис. 3.30, б) вырабатывает сигналы, свидетельствующие об этом (короткие установки в ноль), но на выходе

L Выход VCO

lock flag (внутр.)

INLCK

Рис. 3.30. Захват частоты при перестройке

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 [ 23 ] 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 |